Ise Webpack License Windows 8

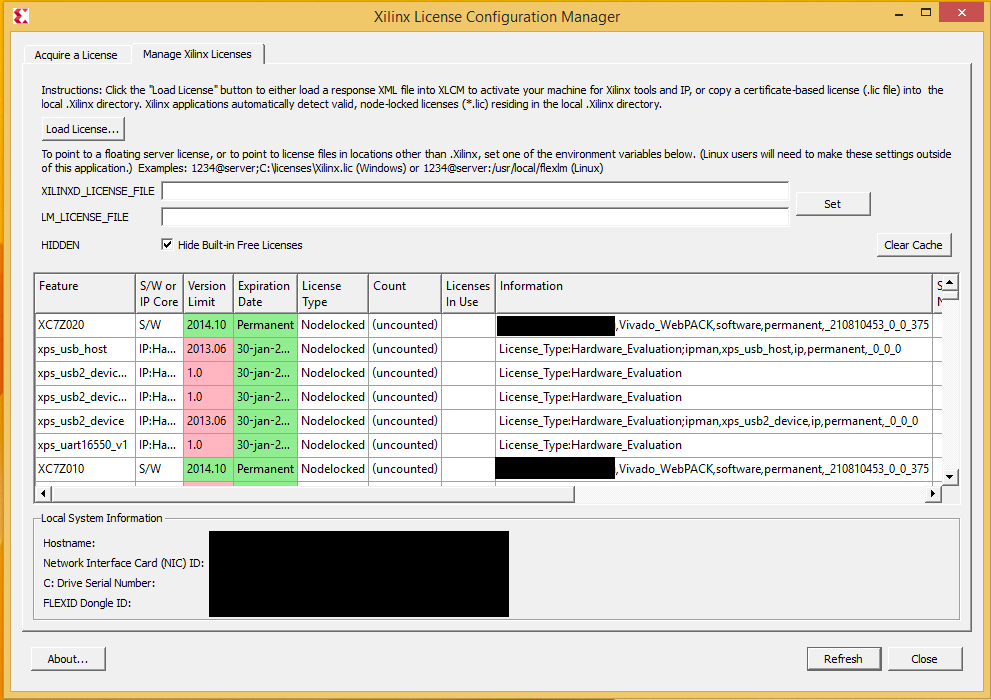

Choose the Get Free ISE WebPack License option and click next. To get your license installed in Windows 8 you need to create a folder in the root of your home. Important Information. ISE Design Suite for Windows 10 supports Spartan®-6 only. For End User License Agreements, please see below: Unified 3rd Party EULA for Win10.

Avast Antivirus Rare here. 14.7 / October 23, 2013; 4 years ago ( 2013-10-23) Development status Superseded by,,, 6.1 Available in Website Xilinx ISE ( Integrated Synthesis Environment) is a software tool produced by for synthesis and analysis of designs, enabling the developer to ('compile') their designs, perform, examine diagrams, simulate a design's reaction to different stimuli, and configure the target device with the. Xilinx ISE is a design environment for FPGA products from Xilinx, and is tightly-coupled to the architecture of such chips, and cannot be used with FPGA products from other vendors. Driver Pci Ven_14e4&dev_4315&subsys_04b514e4&rev_01 Version 10.0. The Xilinx ISE is primarily used for circuit synthesis and design, while ISIM or the logic simulator is used for system-level testing. Other components shipped with the Xilinx ISE include the Embedded Development Kit (EDK), a Software Development Kit (SDK) and ChipScope Pro.

Since 2012, Xilinx ISE has been discontinued in favor of, that serves the same roles as ISE with additional features for development. Xilinx released the last version of ISE in October 2013 (version 14.7), and states that 'ISE has moved into the sustaining phase of its product life cycle, and there are no more planned ISE releases.' Contents • • • • • • • • • User Interface [ ] The primary user interface of the ISE is the Project Navigator, which includes the design hierarchy (Sources), a editor (Workplace), an output console (Transcript), and a processes tree (Processes). The Design hierarchy consists of design files (modules), whose dependencies are interpreted by the ISE and displayed as a. For single-chip designs there may be one main module, with other modules included by the main module, similar to the main() subroutine in programs. Design constraints are specified in modules, which include pin configuration and mapping.